A physical embodiment of a locally-learning neural network, which learns faster than current CPU-based nets.

Problem:

Machine learning is a ubiquitous tool that has found uses in engineering, science, and medicine. Neural networks are some of the most powerful machine learning algorithms, but they train very slowly when they become large. This hampers software pipelines involving data collection, machine learning, and analysis in real-time computing applications. In addition, current CPU and GPU-based neural networks consume vast amounts of electrical power.

Solution:

Designing a physical (circuit-based) neural network that learns using only local information at each node offers fast, scalable, and power-efficient performance. This product leverages the optimization built into the laws of physics to train the neural network on known data. The design is computationally efficient and scalable down to low-power microelectronic applications.

Technology:

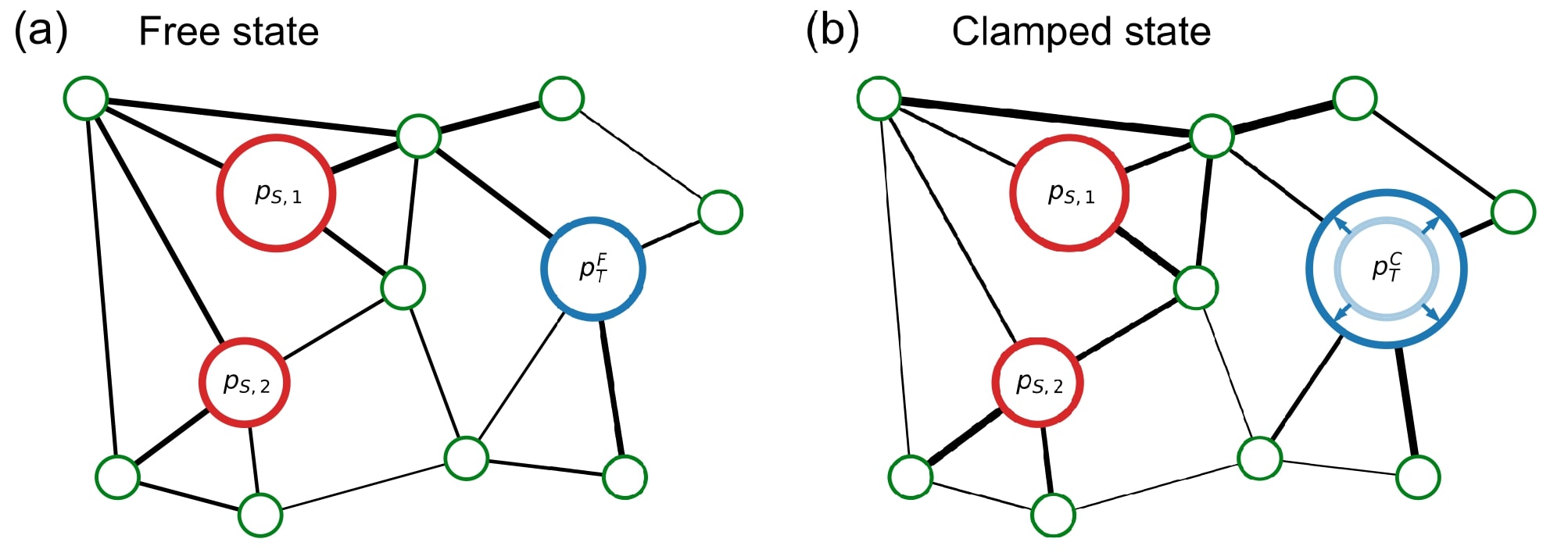

Electrical current follows the most efficient path through a circuit. This built-in optimization inspired the authors to design a locally-learning network of individual circuits. Cycling through “free states” – letting the current follow the easiest path – and “clamped states” – forcing the network to output the correct voltage – settles the network via gradient descent. This finds the optimal network state for a given machine learning application.

Advantages:

- Computes faster than current O(n2) CPU-based methods.

- May physically scale down to microelectronic (10-6 m) scale.

- Current design contains only 15 elements per circuit, and 16 circuits total.

- Low-power, cost-efficient, and robust against damage.

Free (left) and clamped (right) states of the network. The free state sets the voltage at the red nodes and allows the blue node to achieve its natural steady-state voltage. The clamped mode sets all three colored nodes to have specific voltages. Adjusting the resistance of each edge in proportion to its relative power loss trains the network to naturally produce the desired output voltage at the blue node.

Stage of Development:

Proof of Concept

Case ID:

21-9647-tpNCS

Web Published:

10/24/2024

Patent Information:

| App Type |

Country |

Serial No. |

Patent No. |

File Date |

Issued Date |

Expire Date |